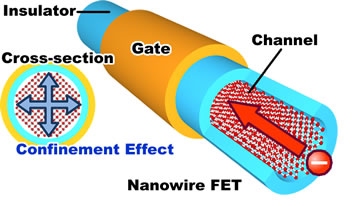

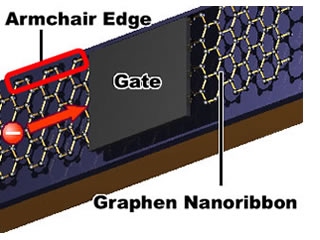

半導体デバイスは、デバイスを小さくすると性能が向上する、「スケーリング則」を信じて微細化が進められてきました。 近年研究されている金属酸化膜半導体(MOS)電界効果トランジスタ(FET)ではゲート長は数10nmまで小さくなっています。 このようなスケールでデバイスを動作させる場合、量子力学的な効果が顕著になってきます。 極めて小さな半導体デバイスでは、量子力学的効果がデバイスの特性を劣化させることもあり、従来のようにデバイスの微細化のみで性能を向上させることは難しくなっています。 そこで、「スケーリング則」による性能向上だけに頼らないような、新しい構造や新しい材料を用いたデバイスが数多く提案、検討されています。 しかし、将来の半導体デバイスの性能予測には、古典的な計算手法では対応することができず、ナノスケールデバイスに現れる物理現象を量子論に基づいて予測できるシミュレータの開発が望まれています。 そこで、私たちの研究グループでは、量子効果が顕著に現れるような、極めて小さい半導体デバイスの性能を予測できるシミュレータを開発することを目的に研究を行っています。 ここでは、私たちが研究しているデバイスの中から、半導体ナノワイヤ、グラフェンナノリボン、スピントランジスタについて説明します。 ナノワイヤ型トランジスタ 次世代のトランジスタとして、ナノワイヤ型の半導体を用いたトランジスタが期待されています。 ナノワイヤ型トランジスタは、従来の平面的なMOSFETと異なり、ワイヤ状のチャネルが全方向から包まれる3次元の構造となっていることが特徴です。 近年の短チャネルのトランジスタでは、ソースとドレインの接近に伴ってドレインの影響がソースにまで及ぶようになり、デバイス特性の劣化の原因の一つとなっています(短チャネル効果)。 これに対して、ナノワイヤ型トランジスタでは全方向からゲート電圧でチャネル内のポテンシャルを制御するため、より応答速度が速く、低消費電力で動作させることが可能なデバイスとして期待されています。 しかし、四方の酸化膜から電子が量子閉じ込め効果の影響を受けるため、チャネル内の電子状態はバルク(半導体結晶の大きな塊)の特性とは異なってきます。 そのため、特性が既知の半導体をチャネルに使ったナノワイヤ型トランジスタであっても、そのデバイス特性はあまりよく分かっていないのが現状です。 私たちは、この強い量子閉じ込め効果を考慮したシミュレータを開発することで、ナノワイヤ型トランジスタの特性を調査しています。 グラフェンナノリボン 2004年、グラファイト(鉛筆の芯)をセロテープではがしたりくっつけたりすることで得られた単層のグラファイトが、非常に高い移動度や量子ホール効果などの興味深い物性を示すことが明らかになりました。 その物質はグラフェンと呼ばれ、炭素原子が蜂の巣のような網の目状に並んだ2次元シートの構造をしています。 グラフェンは電子移動度がシリコンよりも一桁以上高く、デバイスの動作速度を飛躍的に向上させることができるとして、次世代のデバイスの材料として注目を集めています。 グラフェンが示すバンドギャップを持たないとい う性質は、トランジスタのチャネル材料への応用には不向きでしたが、グラフェンを2枚重ねた2層グラフェンや、細長いリボン状に切り取ったグラフェンナノリボンといった構造にすることでバンドギャップを持たせられることが明らかになりました。 2008年にはIBMが実際にグラフェントランジスタの開発に成功したことを発表しています。 私たちは、グラフェンナノリボンを用いたデバイスの性能予測を行い、高いデバイス性能、新たな機能を持つデバイス構造を探求しています。 スピントランジスタ スピントランジスタは、ゲート電極からの電界によって反転層を作り、電子の移動を制御することで動作する従来のMOSFETとは異なり、ゲート電極によって電子のスピンの向きを制御することで動作するトランジスタです。 |